World Semiconductor Test Equipment and ATE Systems Market 2026 Analysis and Forecast to 2035

Executive Summary

The global semiconductor test equipment and ATE (Automated Test Equipment) systems market represents a critical and technologically intensive segment within the broader semiconductor value chain. This market is fundamentally driven by the relentless advancement of semiconductor complexity, where each new process node and architectural innovation demands correspondingly sophisticated testing solutions to ensure yield, performance, and reliability. The analysis for the 2026 edition indicates a market characterized by robust, albeit cyclical, demand, propelled by the proliferation of advanced logic, memory, and heterogeneous integration technologies.

Looking towards the 2035 horizon, the market is poised for transformative shifts, moving beyond traditional volume drivers to address new frontiers in chip design and application. The convergence of artificial intelligence workloads, the expansion of automotive electrification and autonomy, and the persistent demand for high-performance computing are restructuring capital expenditure priorities and test requirements. This evolution necessitates continuous R&D investment from equipment suppliers to deliver systems capable of handling higher pin counts, faster data rates, and more complex power management scenarios within economically viable test times.

This report provides a comprehensive, data-driven assessment of the market's current state, supply-demand dynamics, competitive environment, and price structures. It builds a foundational understanding of the key forces shaping the industry from 2026 onward, offering stakeholders a strategic lens through which to evaluate opportunities, navigate cyclicality, and anticipate the technological inflection points that will define the path to 2035. The analysis underscores that leadership in this market is contingent not merely on hardware capabilities but on integrated software solutions and deep partnerships with leading semiconductor manufacturers.

Market Overview

The semiconductor test equipment market encompasses the hardware and software systems used to verify the functionality and performance of integrated circuits (ICs) before they are shipped to customers. ATE systems form the core of this ecosystem, automated platforms that execute precise electrical tests on wafers (wafer sort) and packaged chips (final test). The market's structure is segmented by the type of device under test, primarily delineated between equipment for testing logic devices (including SoCs, CPUs, GPUs), memory (DRAM, NAND Flash), and analog/mixed-signal/RF chips, each with distinct technical and market characteristics.

Geographically, the market's demand footprint closely mirrors the locations of major semiconductor fabrication (fabs) and outsourced assembly and test (OSAT) facilities. This concentration creates a highly regionalized consumption pattern, with Asia-Pacific, led by Taiwan, South Korea, China, and Japan, accounting for the predominant share of global equipment installations and expenditures. North America and Europe remain significant markets, particularly for R&D-focused and advanced prototyping test systems, often linked to fabless design companies and integrated device manufacturers (IDMs) headquartered in these regions.

The market exhibits pronounced cyclicality, inherently tied to the capital expenditure cycles of semiconductor manufacturers. Periods of aggressive capacity expansion for new technologies, such as the transition to 5nm, 3nm, and beyond, or the build-out of new memory fabs, drive sharp upticks in test equipment demand. Conversely, periods of inventory correction or macroeconomic softening lead to rapid deceleration in order volumes. This cyclical nature requires market participants to maintain agile operations and robust financial management to weather downturns while scaling to meet peak demand.

Demand Drivers and End-Use

Demand for semiconductor test equipment is not monolithic but is propelled by a confluence of application-specific trends. The primary end-use sectors—consumer electronics, data centers, automotive, and industrial—each impose unique requirements on semiconductor performance, which in turn dictate test strategies and equipment specifications. The increasing silicon content per device across all these sectors is a fundamental volume driver, but the qualitative shift in chip architecture is the primary force behind the market's evolution towards more advanced and expensive test platforms.

The proliferation of Artificial Intelligence and Machine Learning, both in the cloud and at the edge, stands as the most potent demand driver for advanced logic test equipment. AI accelerators, GPUs, and high-performance CPUs feature immense die sizes, complex multi-die architectures (chiplets), and unprecedented power delivery networks. Testing these devices requires ATE with exceptionally high parallelism, sophisticated power management units (PMUs), and advanced thermal control to handle the immense heat generated during test. Furthermore, the need to test for specific AI workload performance adds a new layer of software-defined test complexity.

Automotive semiconductor demand is undergoing a radical transformation, acting as a major driver for both volume and reliability-focused test solutions. The shift towards electric vehicles (EVs) increases the demand for power management ICs (PMICs) and insulated-gate bipolar transistors (IGBTs), while advanced driver-assistance systems (ADAS) and autonomous driving require high-performance SoCs, sensors (LiDAR, radar), and memory. These automotive-grade chips require test protocols that guarantee functional safety and extreme reliability over extended temperature ranges and product lifetimes, necessitating specialized test hardware and rigorous procedures.

The memory market, particularly for DRAM and NAND Flash, remains a significant but volatile driver. Transitions to new architectures like DDR5, LPDDR5, and 3D NAND with increasing layer counts require new test cell technologies capable of handling faster data rates and more complex cell structures. Demand here is closely tied to data center expansion and consumer electronics refresh cycles, leading to sharp, synchronized investment waves in memory test equipment across a concentrated supplier base.

- AI/ML and HPC: Driving demand for high-speed, high-parallelism testers for complex SoCs and accelerators.

- Automotive Electrification & Autonomy: Increasing demand for reliable, high-voltage analog/power and high-performance compute test solutions.

- 5G/6G and Connectivity: Propelling need for advanced RF test systems for mmWave and sub-THz frequencies.

- Advanced Packaging & Heterogeneous Integration: Requiring new test methodologies for chiplets, 2.5D/3D stacking, and system-in-package (SiP) designs.

- IoT Proliferation: Generating volume demand for low-cost, efficient test handlers and contactors for MCUs and connectivity chips.

Supply and Production

The global supply chain for semiconductor test equipment is highly specialized and concentrated among a limited number of technologically dominant players. The industry is characterized by significant barriers to entry, including decades of accumulated intellectual property, deep software algorithm expertise, and entrenched customer relationships that are built on long-term collaboration on next-generation node development. Production is capital-intensive, requiring cleanroom facilities and precision engineering capabilities, but is generally less centralized geographically than wafer fabrication equipment, with key manufacturing clusters in Japan, the United States, and Southeast Asia.

A critical aspect of the supply landscape is the intricate ecosystem of subsystems and components. Leading ATE vendors often act as system integrators, sourcing critical components such as high-performance pin electronics, advanced load boards, device interface boards (DIBs), and robotic handlers from a network of specialized suppliers. Disruptions in this sub-supply chain, whether from geopolitical tensions, logistical bottlenecks, or single-source dependencies, can significantly impact the lead times and production capacity of final ATE systems. The industry has been actively diversifying sources and increasing inventory buffers for key components in response to recent global supply chain volatility.

Research and Development investment is the lifeblood of this industry, with leading companies typically reinvesting a substantial percentage of their revenue back into R&D. This investment is directed towards developing new test methodologies for upcoming process nodes (e.g., sub-2nm), creating software tools for faster test program development and data analytics, and designing hardware capable of testing emerging technologies like silicon photonics or quantum computing chips. The ability to co-develop test solutions in lockstep with leading-edge semiconductor manufacturers provides a formidable competitive moat.

Trade and Logistics

International trade is the default mode of operation for the semiconductor test equipment market, given the geographic disparity between major production sites and end-user fabs. The movement of these high-value, sensitive, and often large-scale systems involves complex logistics, including air freight for critical components and sea freight for complete systems. Customs clearance, export controls, and compliance with international regulations, particularly those concerning dual-use technologies, are paramount considerations for market participants. Delays or denials in export licenses can directly impact a supplier's ability to fulfill contracts in key markets.

The geopolitical landscape has introduced new layers of complexity to trade flows. Export control regimes, particularly those targeting advanced technology, have reshaped market access in certain regions. This has led to the emergence of parallel supply chain strategies, where equipment vendors may develop differentiated product lines or feature sets to comply with varying international trade regulations. Furthermore, regional government incentives for domestic semiconductor production, such as those enacted in the United States, European Union, and China, are influencing the final destination of equipment shipments, potentially altering traditional trade patterns over the forecast period to 2035.

After-sales service, support, and spare parts logistics constitute a critical, high-margin segment of the business model. The need for rapid on-site engineering support, preventative maintenance, and just-in-time delivery of proprietary spare parts requires a globally distributed service network with localized inventory hubs. The efficiency and reliability of this service logistics network are key differentiators for equipment vendors, as semiconductor manufacturers cannot afford extended tool downtime given the immense capital cost of idled fabrication lines.

Price Dynamics

Pricing in the semiconductor test equipment market is not standardized but is highly negotiated and varies dramatically based on system configuration, performance specifications, and the depth of the customer relationship. A high-end ATE system for testing advanced 3nm SoCs or HBM memory can command a price point orders of magnitude higher than a tester for mature-node analog chips. The price is a function of the embedded R&D cost, the bill of materials for advanced components, and the value proposition it delivers in terms of test time reduction, yield improvement, and capability to handle next-generation devices.

The market exhibits a clear trend towards increasing average selling prices (ASPs) for leading-edge equipment. This is driven by the escalating technical requirements: more pins, higher data rates (exceeding 100 Gbps per pin), integrated photonics testing, and advanced thermal management systems all contribute to higher hardware costs. Furthermore, the value of the proprietary software—including test program compilers, debug tools, and data analytics suites—comprises an ever-larger portion of the total system price, reflecting the shift from pure hardware to integrated software-hardware solutions.

However, this upward pressure on high-end ASPs coexists with intense pricing competition in the market for mature and mainstream test equipment. In segments where technology is standardized and alternatives exist, price becomes a significant competitive lever. Additionally, the growing secondary market for refurbished and re-certified equipment provides a cost-effective alternative for testing legacy or mature technology nodes, creating a pricing ceiling for new equipment in those segments. This bifurcated pricing environment requires vendors to strategically manage their product portfolios across the technology spectrum.

Competitive Landscape

The competitive landscape is an oligopoly, dominated by a handful of global players with comprehensive product portfolios across logic, memory, and analog test. These companies compete on the basis of technological leadership, product performance and reliability, total cost of ownership (TCO), global support networks, and the strength of their strategic partnerships with key semiconductor manufacturers. Competition is most intense at the leading edge of technology, where being selected as the "tool of record" for a new process node can lock in revenue for an entire generation of chip production.

Beyond the broad-line ATE giants, the market includes several successful "best-in-class" specialists. These companies focus on specific niches, such as RF test, power device test, or memory test, where they can offer superior technical performance or a more cost-optimized solution than the generalist players. The competitive dynamics also involve a layer of subsystem and component suppliers who provide critical technologies like advanced probe cards, high-speed connectors, and test handlers; innovation at this component level can directly influence the performance and market success of the integrated ATE platforms.

- Advantest Corporation: A global leader, particularly strong in SoC and memory test, with a dominant position in DRAM test equipment.

- Teradyne, Inc.: A major force in logic, SoC, and storage test, with significant market share in testers for automotive and industrial applications.

- Others: The landscape includes other significant players and strong niche competitors in areas like analog/mixed-signal test, RF test, and photonics test.

Strategic initiatives in the competitive arena increasingly focus on software and data. Companies are investing heavily in AI-driven test program generation, yield analysis software, and fleet management tools that provide insights across a customer's entire test floor. The ability to offer a seamless data ecosystem from design verification through volume production test is becoming a key battleground, as semiconductor makers seek to compress development cycles and improve overall equipment effectiveness (OEE).

Methodology and Data Notes

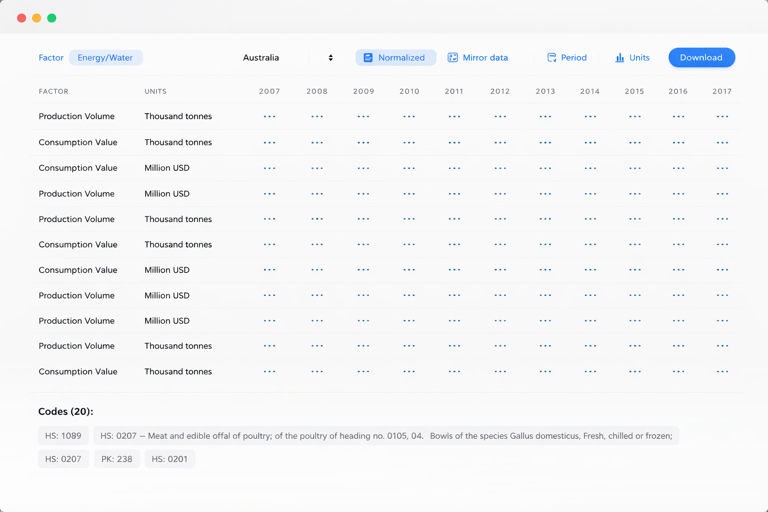

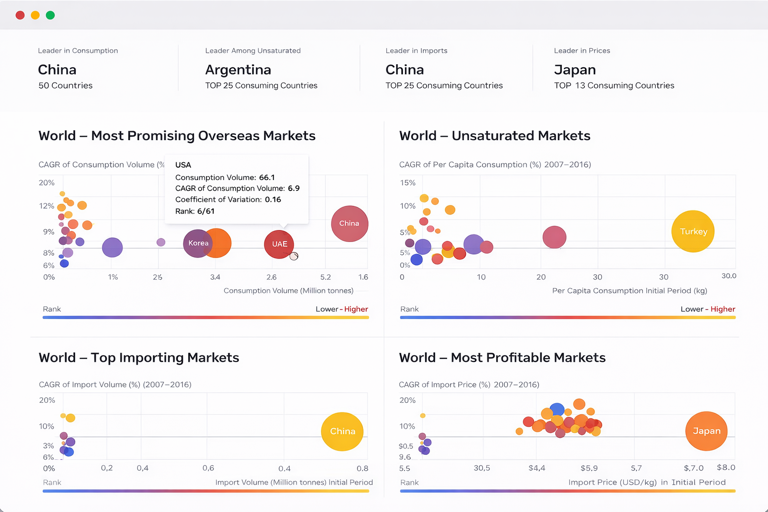

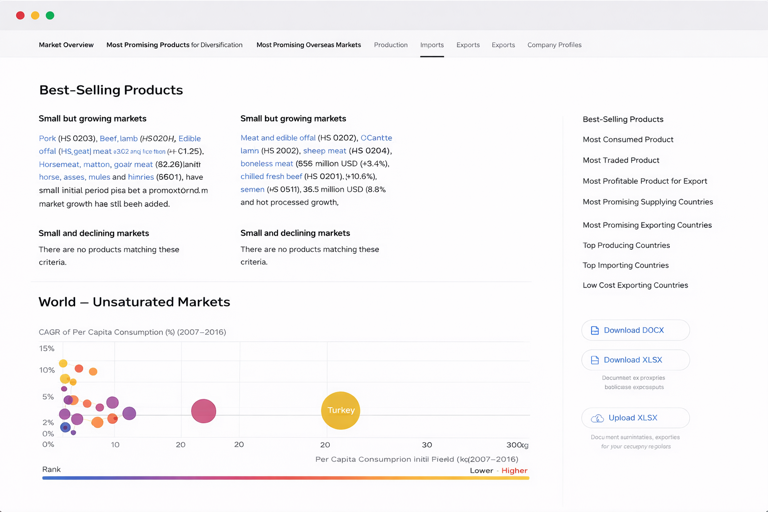

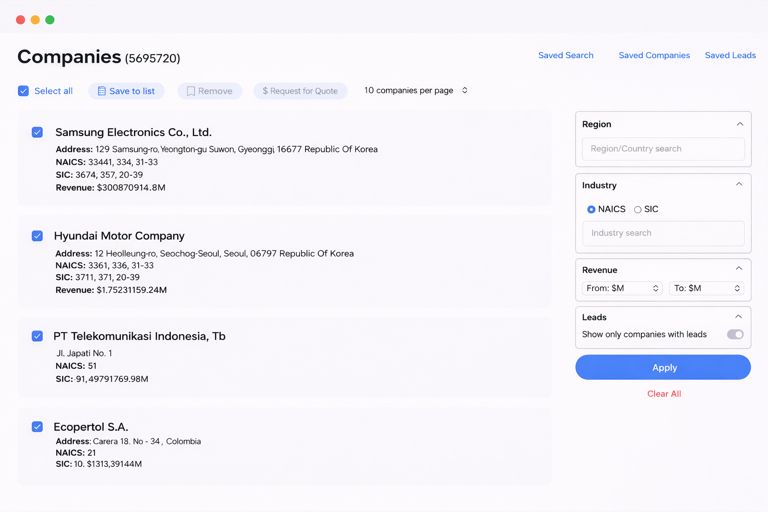

This report is constructed using a multi-faceted research methodology designed to ensure analytical rigor, accuracy, and strategic relevance. The foundation is a comprehensive review and synthesis of primary data sources, including official government and international trade statistics, financial disclosures and annual reports from publicly traded companies across the semiconductor value chain, and regulatory filings. This primary data is triangulated with technical literature, patent analysis, and industry benchmark studies to validate trends and quantify market sizes.

The core analytical framework employs a combination of top-down and bottom-up modeling. Top-down analysis assesses the macro-economic and capital expenditure environment for the semiconductor industry, using leading indicators to forecast investment cycles. Bottom-up analysis involves modeling demand from specific device segments (e.g., units of 5nm SoCs, terabytes of NAND Flash), applying estimated test equipment intensity per wafer or per unit, and aggregating to a total market view. This dual approach allows for cross-verification of estimates and identification of discrepancies that may signal emerging trends.

Forecasting to the 2035 horizon involves scenario analysis to account for the high degree of uncertainty inherent in a technology-driven, cyclical market. Multiple scenarios are developed based on different trajectories for key variables such as the pace of AI adoption, geopolitical trade policies, and the commercial rollout of disruptive technologies like quantum computing. The report clearly delineates between observed historical data, near-term projections based on announced capex, and long-term scenario-based forecasts, ensuring transparency regarding the assumptions underlying each view.

All market size estimates and forecasts are presented in constant U.S. dollars to remove the effects of currency fluctuation and inflation, providing a clear view of real market growth. The report explicitly notes the boundaries of its analysis, specifying the included and excluded product categories (e.g., including probe cards and handlers as part of the test cell, excluding burn-in ovens). Any data limitations, such as gaps in certain regional trade data or the aggregation of product categories in public financials, are clearly acknowledged, and the methodological adjustments made to address them are explained.

Outlook and Implications

The outlook for the world semiconductor test equipment and ATE systems market from the 2026 vantage point towards 2035 is one of sustained strategic importance coupled with accelerating technological change. The market is expected to grow in alignment with, and potentially at a premium to, the overall semiconductor capital equipment market, as the value of test as a percentage of total chip cost continues to rise for advanced devices. This growth, however, will not be linear but will manifest as a series of step functions aligned with major industry inflection points, such as the widespread adoption of gate-all-around transistors, the commercialization of 3D stacked logic, and the maturation of new memory technologies.

For equipment suppliers, the strategic implications are profound. Success will require a dual-track approach: maintaining relentless execution and technological leadership in core ATE businesses while aggressively investing in adjacencies. The most significant opportunities lie in the software domain—providing intelligent, data-driven solutions for test optimization, predictive maintenance, and yield learning. Furthermore, the test challenges posed by heterogeneous integration and chiplets will blur the lines between traditional test, wafer-level metrology, and assembly processes, creating openings for new integrated solutions and partnerships.

For semiconductor manufacturers and OSATs, the implications center on total cost of test and strategic supplier management. The increasing capital cost of leading-edge test cells will necessitate more sophisticated financial models and a sharper focus on equipment utilization and throughput. Diversifying the supplier base for critical test technologies, while deepening collaborative relationships with key partners for co-development, will be a delicate balancing act. Investing in internal test engineering talent and data science capabilities will be crucial to fully leverage the capabilities of next-generation ATE systems.

Finally, for investors and policymakers, the market underscores the critical, enabling role of test equipment in the entire semiconductor ecosystem. Geopolitical efforts to build resilient semiconductor supply chains must account for the concentration and essential nature of this segment. Investment in domestic R&D for test technologies, support for workforce development in test engineering, and the facilitation of global trade for these critical tools will be key determinants in shaping the competitive landscape of the global semiconductor industry on the path to 2035.